#### Reachability Analysis Using Octagons

Andrew N. Fisher and Chris J. Myers

Department of Electrical and Computer Engineering University of Utah

FAC 2014 July 9, 2014

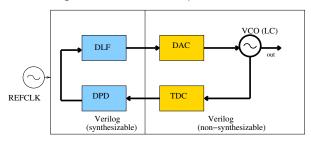

#### Digitally Intensive Analog Circuits

• Digitally intensive analog circuits attempt to replace analog components with digital ones whenever possible.

- Result is optimized power efficiency and performance as well as improved robustness to process variability.

- These circuits though further complicate the verification problem.

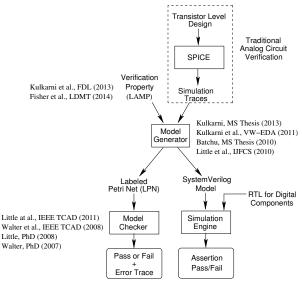

#### Simulation-Based Verification

- Digital verification typically uses switch or RTL-level simulations.

- AMS verification uses detailed transistor-level (SPICE) simulations.

- SPICE simulation of a PLL can take weeks or even months.

- Long simulation time makes system-level simulation difficult.

- Functional bugs can be missed resulting in catastrophic failures.

## **Analog Verification**

Sandipan Bhanot CEO of Knowlent

If the digital designers did verification the way analog designers do verification, no chip would ever tape out. (DACezine, January 2008)

#### Model Checking

- Model checking uses non-determinism and state exploration to formally verify designs over all possible behaviors.

- Has had tremendous success for verifying of both digital hardware and software systems (now routinely used at Intel, IBM, Microsoft, etc.).

- For AMS circuits, it is a promising mechanism to validate designs in the face of noise and uncertain parameters and initial conditions.

- AMS verification is complicated by the need to:

- Construct abstract formal models of the AMS circuits.

- Specify formal properties that are to be verified.

- Represent continuous variables efficiently (voltages, currents, and time).

#### Model Checking

- *Model checking* uses non-determinism and state exploration to formally verify designs over all possible behaviors.

- Has had tremendous success for verifying of both digital hardware and software systems (now routinely used at Intel, IBM, Microsoft, etc.).

- For AMS circuits, it is a promising mechanism to validate designs in the face of noise and uncertain parameters and initial conditions.

- AMS verification is complicated by the need to:

- Construct abstract formal models of the AMS circuits. (FAC 2011)

- Specify formal properties that are to be verified. (FAC 2013)

- Represent continuous variables efficiently (voltages, currents, and time).

#### **Zones**

- Used for formal verification of timed automata and time(d) Petri nets.

- Simple geometric polyhedra formed by the intersection of hyper-planes representing inequalities of the form  $y x \le c$ .

- Implies polyhedra with only  $0^{\circ}$ ,  $90^{\circ}$ , and positive  $45^{\circ}$  angles.

- For timed systems, all variables evolve at a rate of 1, and zone evolves along a positive 45° angle.

- Algorithms to restrict, project, and advance time are fast and simple.

- Can use Floyd's all pairs shortest-path algorithm to construct a canonical maximally tight representation.

- Conveniently represented using a difference bound matrix (DBM).

#### **Zones**

$$y - t0 \le M_y$$

$x - t0 \le M_x$

$t0 - x \le -m_x$

$t0 - y \le -m_y$

$y - x \le b_1$

$x - y \le -b_2$

$t0 \quad x \quad y$

$t0 \begin{pmatrix} 0 & M_x & M_y \\ -m_x & 0 & b_1 \\ -m_y & -b_2 & 0 \end{pmatrix}$

#### **Zones**

$$y - t0 \le 3$$

$$x - t0 \le 3$$

$$t0 - x \le 0$$

$$t0 - y \le 0$$

$$y - x \le 1$$

$$x - y \le 1$$

$$t0 \quad x \quad y$$

$$0 \quad 0 \quad 3 \quad 3$$

$$0 \quad 0 \quad 1$$

$$0 \quad 1 \quad 0$$

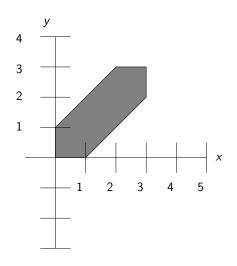

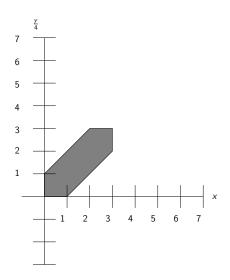

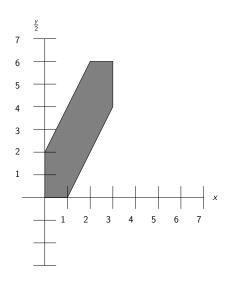

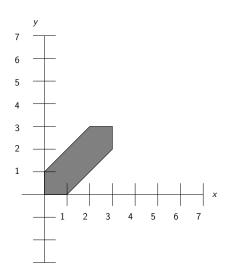

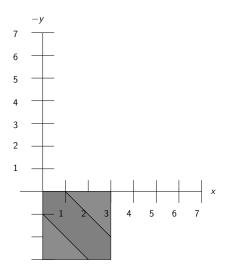

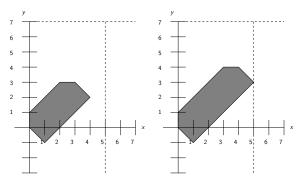

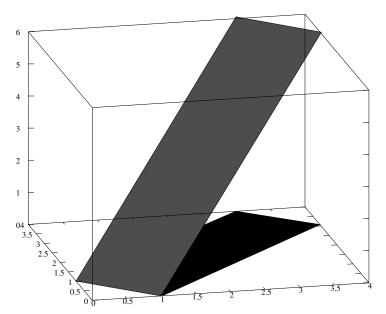

#### Zone Warping

- To verify AMS circuits, need variables that evolve at non-unity rates.

- Zones can be used with a variable substitution.

- Replace variable v with non-zero rate r with a variable  $\frac{v}{r}$ .

- The new variable  $\frac{v}{r}$  evolves at a rate of 1.

- Resultant polyhedra is no longer a zone.

- Warping creates the smallest zone that contains it.

# Positive Zone Warping

# Positive Zone Warping

# Positive Zone Warping

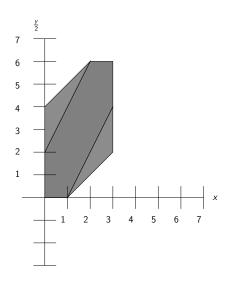

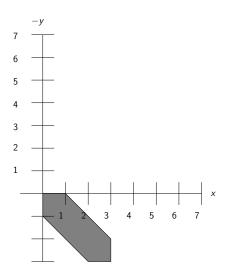

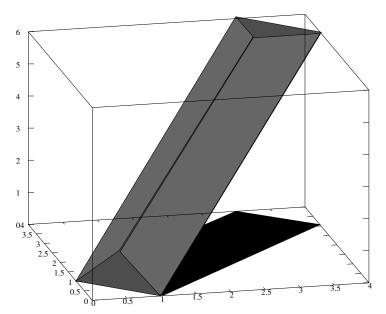

# Negative Zone Warping

# Negative Zone Warping

# Negative Zone Warping

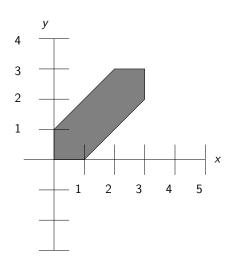

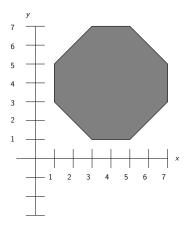

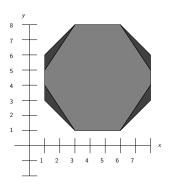

#### Octagons

ullet Extension of zones that allow negative 45° degree angles.

#### Octagon DBM

• Can be represented using a DBM (Mine, 2001) and manipulated with efficient algorithms.

$$x^{+} - x^{-} \le 2M_{x}$$

$x^{-} - x^{+} \le -2m_{x}$

$y^{+} - y^{-} \le 2M_{y}$

$y^{-} - y^{-} \le -2m_{y}$

$$x^{+} - x^{-} \leq 2M_{x} \qquad x^{+} \qquad x^{-} \qquad y^{+} \qquad y^{-}$$

$$x^{-} - x^{+} \leq -2m_{x} \qquad x^{-}$$

$$y^{+} - y^{-} \leq 2M_{y} \qquad y^{+}$$

$$y^{-} - y^{-} \leq -2m_{y} \qquad y^{-}$$

$$x^{+} - x^{-} \qquad y^{+} \qquad y^{-}$$

$$2M_{x} \qquad 0$$

$$y^{+} \qquad 0$$

#### Octagon DBM

• Can be represented using a DBM (Mine, 2001) and manipulated with efficient algorithms.

$$y^{+} - x^{+} \le b_{1}$$

$x^{-} - y^{-} \le b_{1}$

$y^{-} - x^{-} \le -b_{2}$

$x^{+} - y^{+} \le -b_{2}$

$y^{+} - x^{-} \le b_{3}$

$x^{+} - y^{-} \le b_{3}$

#### Reachability Analysis Using Octagons

- Utilized for software checking, and efficient restriction, projection, and constraint tightening algorithms have been developed.

- New algorithms are needed to add new continuous variables, advance time, and warp the octagon.

#### Adding Variables to Octagons

- Adding new continuous variables and clocks is simply a matter of re-interpreting the algorithms for zones in the language for octagons.

- When adding a continuous variable v with rate r, the maximum and minimum values for v are divided by r and added to the DBM (after multiplying by 2).

- Relational entries are set to infinity, indicating no relationship.

#### Octagon Time Advancement

- Extend the octagon along the 45° lines.

- For zones, to advance time, simply set the upper bounds for all the variables to the maximum allowed value before an event occurs.

- For octagons, -45° line slicing the upper right hand corner has a limiting effect on the upper bounds of the two variables involved.

- Entries associated with inequalities  $y + x \le c$  must also be set to their maximum allowed value in relation to the maximums of x and y.

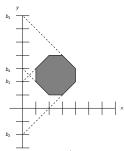

#### Octagon Warping

- Again replace every variable v by  $\frac{v}{r}$  where r is the rate of v.

- Replace resulting polyhedra with smallest octagon that contains it.

- Accomplished by using a few algebraic equations that determine where the new axis intercepts are in terms of the old intercept values.

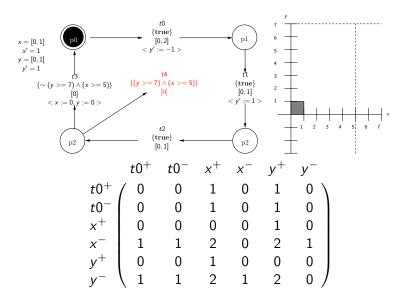

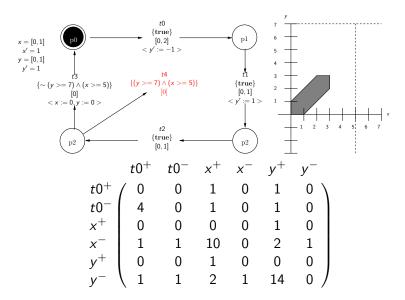

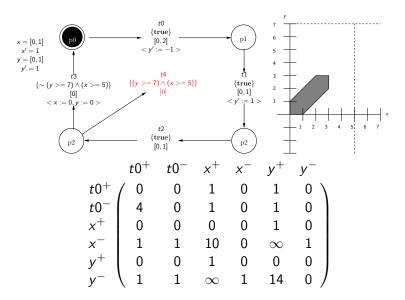

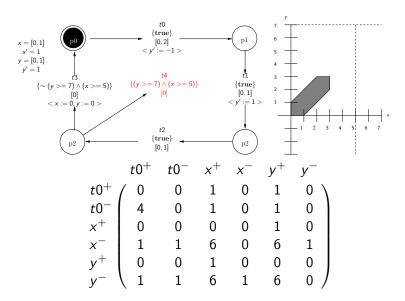

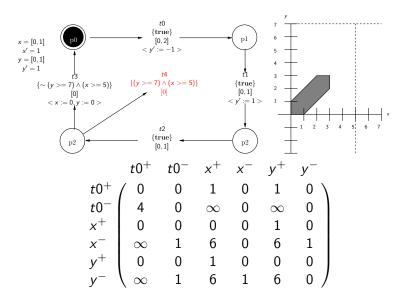

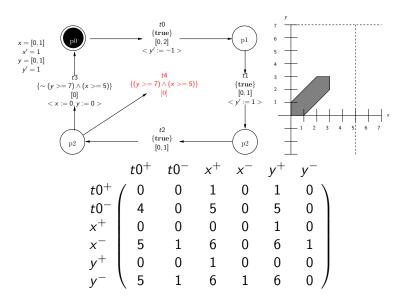

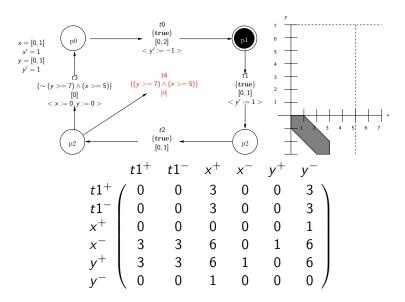

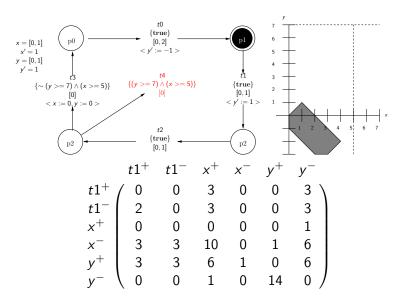

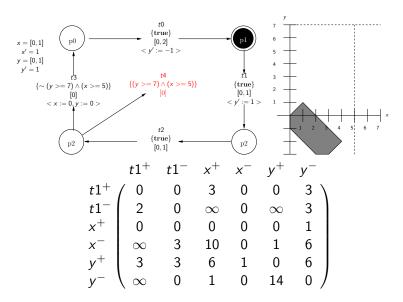

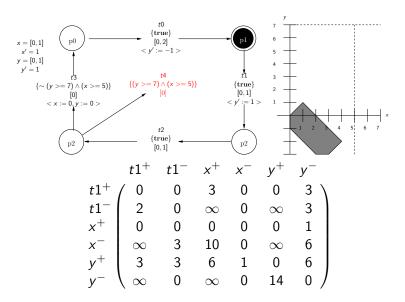

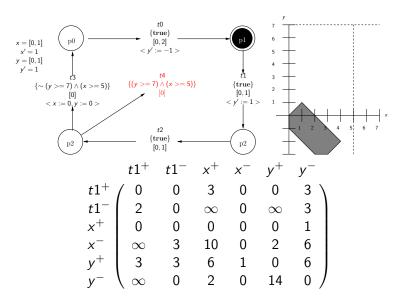

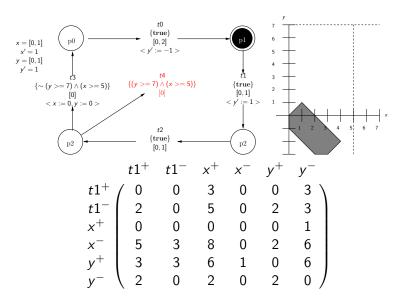

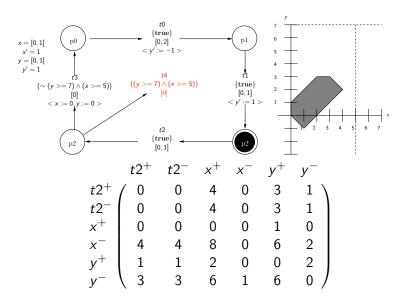

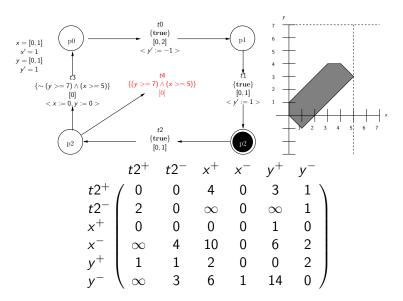

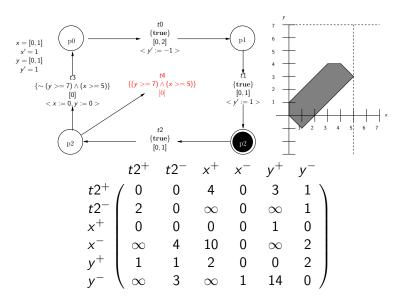

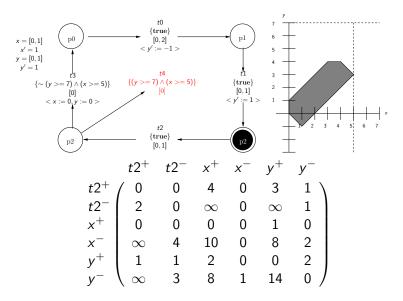

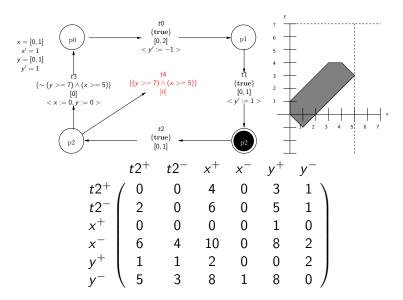

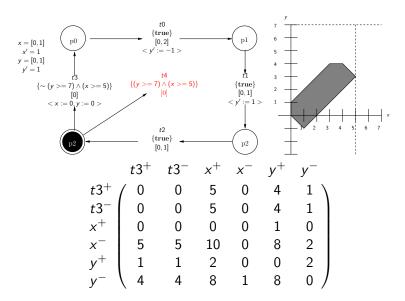

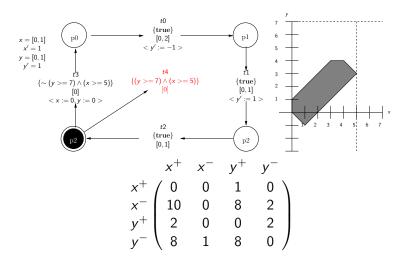

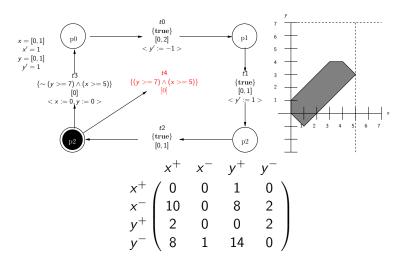

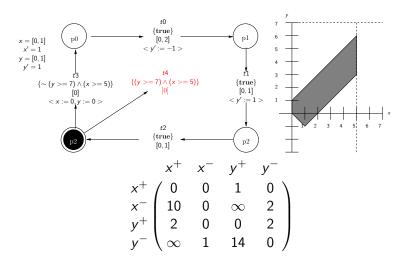

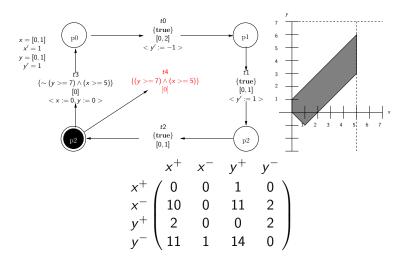

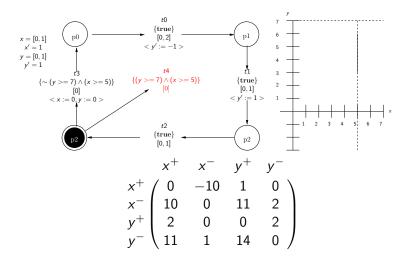

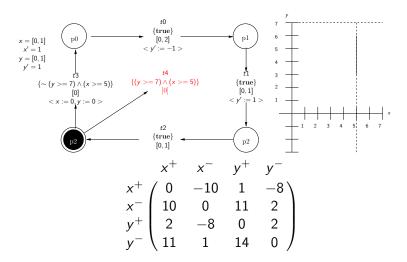

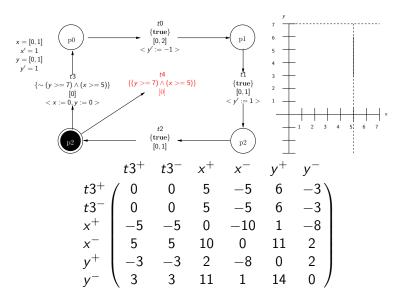

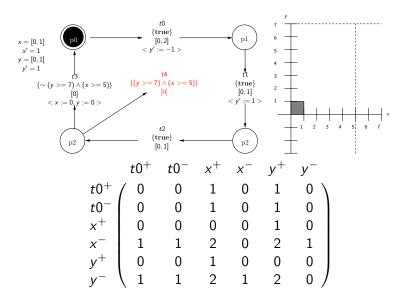

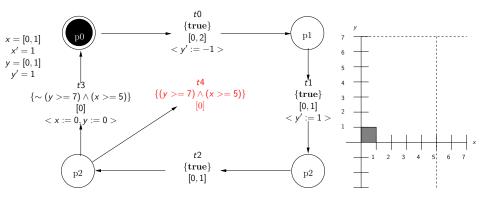

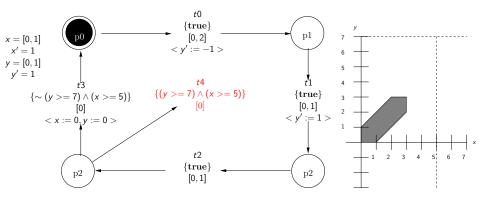

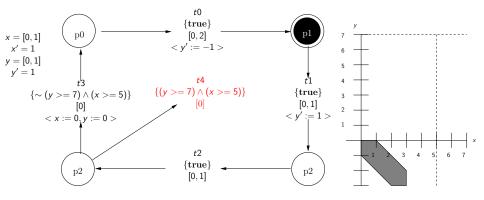

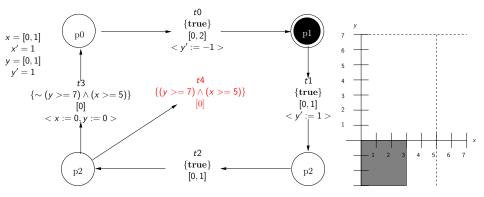

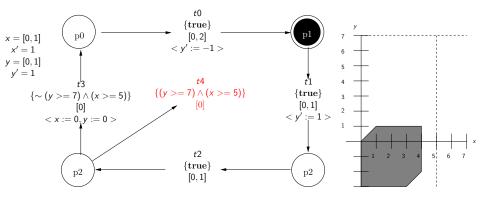

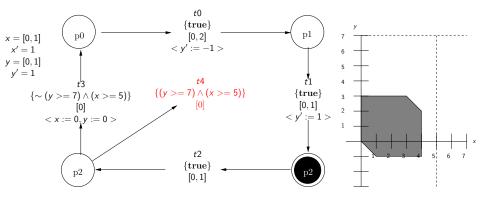

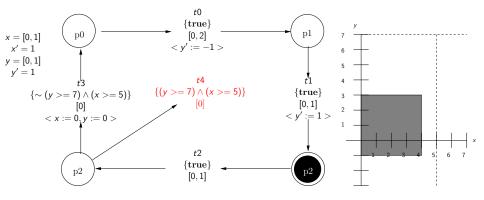

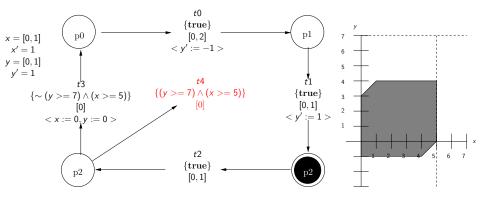

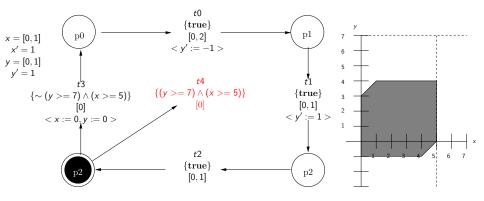

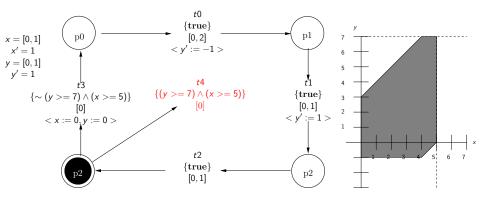

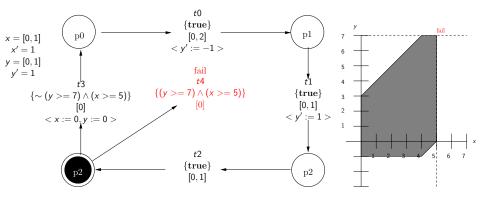

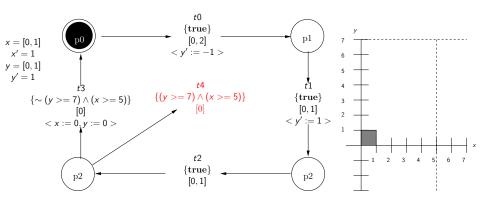

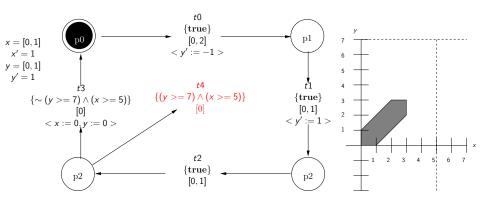

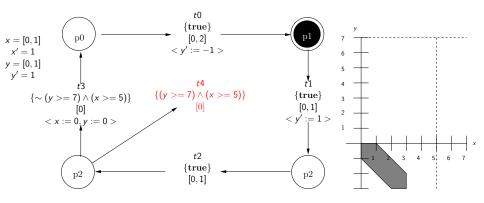

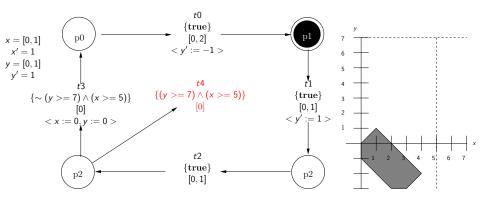

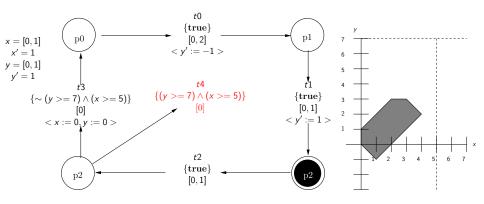

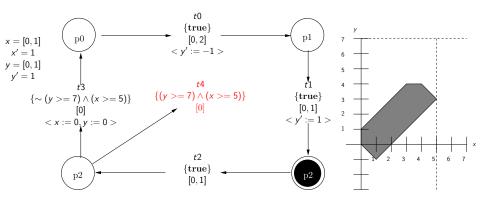

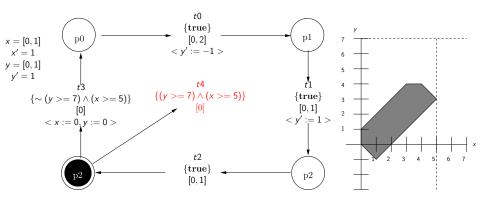

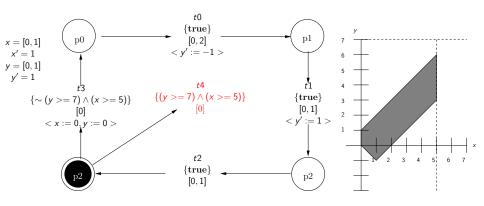

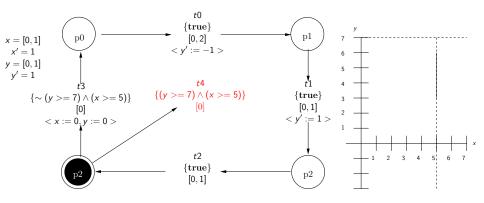

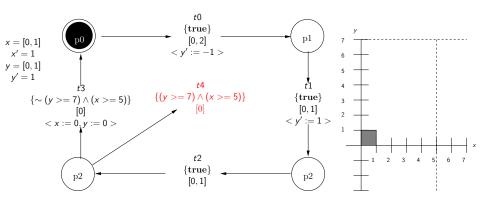

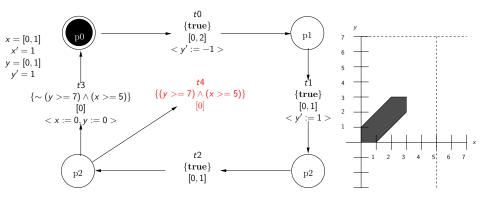

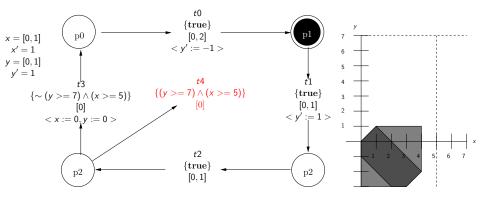

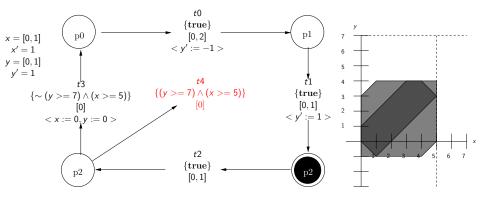

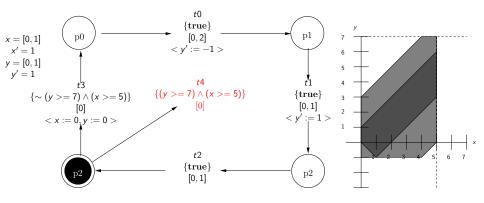

#### Octagon Example

#### Octagon Example

# False Negatives

- Octagons do not eliminate the possibility of false negatives even in the case where rates are only  $\pm 1$ .

- Time advancement also introduces a degree of over-approximation, related to the negative 45° lines.

- Advancement in three dimensions of one of these negative  $45^{\circ}$  line segments belongs to a plane of the form ax + by + cz = d.

- The bounding hyper-planes are of the form  $\pm v_i \pm v_j \leq c$  and not able to capture this plane produced by advancing time.

# False Negative Example

# False Negative Example

# LEMA: LPN Embedded Mixed-Signal Analyzer

Fisher et al., MWSCAS (2014)

# Acknowledgements

Satish Batchu (Qualcomm)

Andrew Fisher (Utah)

Kevin Jones (Aberdeen)

Dhanashree Kulkarni (Intel)

Scott Little (Intel)

David Walter (Virginia State)

Supported by SRC Contracts 2002-TJ-1024, 2005-TJ-1357, 2008-TJ-1851, NSF Grant CCF-1117515, and by Intel Corporation.