# **Electronic Design Automation (EDA)**

## Zellerzeugung

Zellerzeugung

Standardzellen

Standardzellen Beispiele

Manueller Entwurf

Kopplung Schematic/Layout

Zellgeneratoren

Physikalische Parametrierung

Funktionale Parametrierung

Date of generation: 26.4.2022

## Zellerzeugung: Zellerzeugung

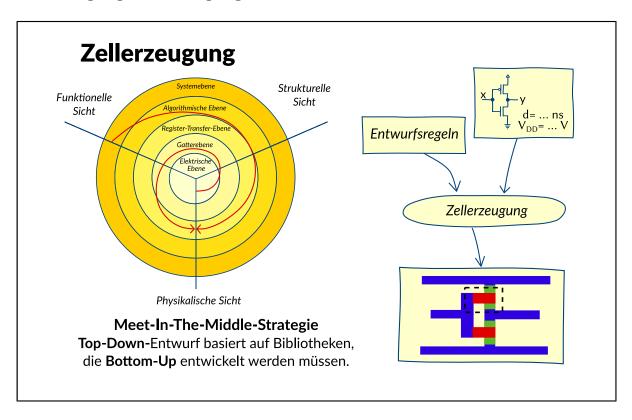

Um einen Meet-In-The-Middle Entwurfsablauf durchführen zu können, sind für alle Komponenten der "Mittelebene" (in der Regel die Gatterebene) Bibliothekselemente zur Verfügung zu stellen, die alle für den Entwurf erforderlichen Informationen in allen Sichten enthalten (Bibliotheksentwurf). Insbesondere muss für jede Komponente ein Layout vorhanden sein. Auf Gatterebene verwendet man in der Regel so genannte Standardzellen.

#### Zellerzeugung: Standardzellen

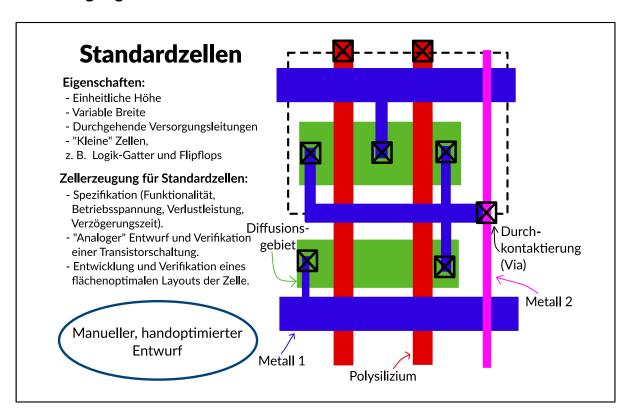

Standardzellen sind durch eine einheitliche Bauhöhe gekennzeichnet, so dass sie sich in Reihen aneinander ordnen lassen und zu einem einfachen Verdrahtungsschema führen. Die Breite der Zellen variiert entsprechend ihrer Komplexität. Die Verdrahtung der Versorgungsspannungen vereinfacht sich stark; durch Aneinanderfügen sind die Versorgungsspannungen verschiedener Zellen verbunden. Die logischen Anschlüsse der Zellen werden an einer oder beiden Seiten herausgeführt. Auch diese können später leicht angeschlossen werden. Diese Struktur eignet sich jedoch nur für kleine Zellen, wie Gatter, Register, Zähler u.ä. Größere Blöcke, wie Speicher, passen nicht in das Strukturschema einer einheitlichen Bauhöhe und können daher nur separat realisiert werden. Dieses Problem wird bereits im Floorplanning betrachtet.

Zunächst ist für jede Zelle eine Spezifikation zu erstellen. Neben der Grundfunktionalität des Gatters z.B. NAND oder NOR-Gatter sind Betriebsspannung, Verlustleistung und z.B. Verzögerungszeit zu spezifizieren. Nun wird für jede Zelle eine Transistorschaltung entwickelt und verifiziert, die die geforderten Eigenschaften erfüllt. Schließlich sind die Layouts für diese Zellen zu entwickeln. Diese werden dann in der Bibliothek zur Verwendung von Platzierungs- und Verdrahtungswerkzeugen abgelegt.

Das Layout einer Zelle selbst sollte auf Grund seiner häufigen Verwendung flächenoptimiert sein. Aus diesem Grund werden diese Layouts in der Regel manuell erstellt.

## Zellerzeugung: Standardzellen Beispiele

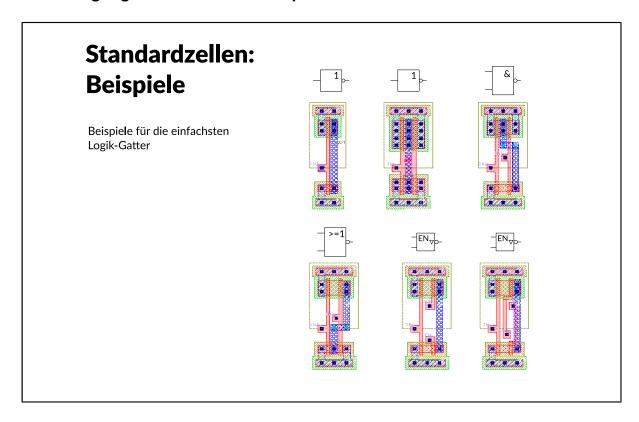

Hier sind einige einfache Standardzellen von einfachen Logikgattern aufgeführt. In typischen Bibliotheken sind ca 50-200 solcher (meist etwas komplexerer) Standardzellen enthalten. In unserem Beispiel sind zwei Inverter mit unterschiedlicher Stärke (Fan Out), je ein NAND und NOR Gatter sowie zwei Tristate-Treiber, die die gleiche Funktion, aber unterschiedliche Anschlusslagen zur Verdrahtung aufweisen.

#### Zellerzeugung: Manueller Entwurf

Ist es bei endlicher Komplexität erforderlich, die Chipfläche zu optimieren, ist nach wie vor der Mensch allen automatischen Verfahren überlegen. Für viele Anwendungen (Standard , Analogschaltungen, Zellentwurf) sind deshalb nach wie vor manuelle Verfahren dominierend, d.h. die detaillierte Geometrie aller Masken wird vom Menschen entworfen. Die Arbeitstechnik hat sich dabei seit den 60er Jahren über die Verwendung von Bleistift und Radiergummi, über die Digitalisierung von Handentwürfen sowie den ersten an Großrechner angeschlossenen Grafiksystemen (Calma, Computervision) zu interaktiven intelligenten Grafikeditoren auf Workstations entwickelt. Dem Layouter stehen dort geometrische Grundstrukturen zur Verfügung, die er abrufen und durch verschiedene Operationen manipulieren kann (verschieben, drehen, skalieren, löschen, usw.) Der Entwurf arbeitet polygonbasiert.

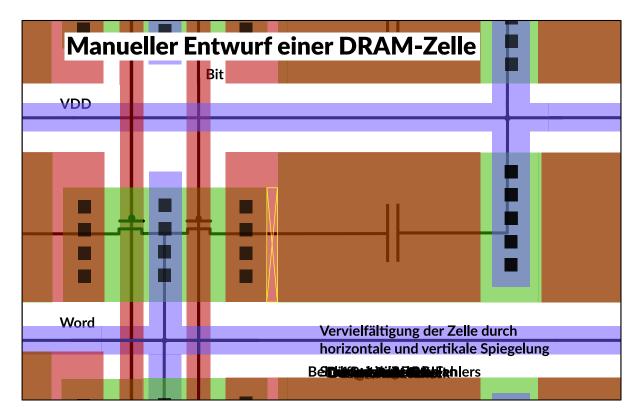

Im Beispiel der DRAM-Zelle werden zuerst die Drain-, Gate- und Source-Gebiete des Transistors durch Wahl der Diffusiongebiete bestimmt. Zusätzlich wird eine Diffusionsfläche für den Speicherkondensator der DRAM-Zelle benötigt. Das Gate wird in Polysilizium realisiert (Bit-Leitung). Mit Metall-Flächen und Kontakten zwischen den Layern wird die Zelle verdrahtet. Es muss beim Erstellen auf Symmetrie geachtet und dafür gesorgt werden, dass mehrere Zellen leicht zu matrixförmig aufgebauten Speichern zusammengeschaltet werden können. Dazu sind die Wort- und Bitleitungen an den Kanten herauszuführen.

Nachdem die Zelle gelayoutet wurde, können im Layout-Editor noch Prüfungen stattfinden. Zum einen muss die Schaltung gegen die Netzliste geprüft werden. Zum anderen müssen die Entwurfsregeln überprüft, d.h. der Design-Rule-Check(DRC) durchgeführt werden. Dies geschieht in der Regel interaktiv, indem nach Aufruf des DRCs die Fehler als blinkende Elemente im Layout grafisch dargestellt werden und so leicht beseitigt werden können.

Durch vertikale und horizontale Spiegelung entsteht aus einer DRAM-Zelle ein Feld von Speicherzellen.

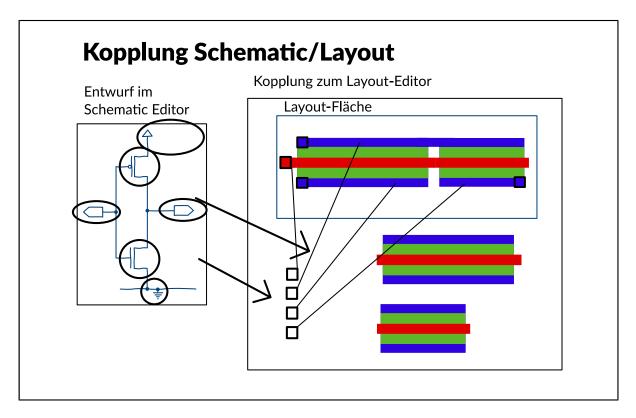

#### **Zellerzeugung: Kopplung Schematic/Layout**

Eine bessere Unterstützung des Designers kann durch eine Kopplung des Schematics mit dem Layout erreicht werden. Für den Standardzellenentwurf, aber auch für den Entwurf von analogen Zellen wird in der Regel eine solche Kopplung verwendet. Im Bild ist zunächst nur der Schaltplan vollständig vorhanden. Es wird eine neue Layoutfläche erstellt (rechts im Bild). Auf diese werden die Bauelemente des Schaltplans automatisch als Layout platziert. Die Elemente können aus einer Bibliothek stammen oder als parametrierte Zellen direkt aus den Spezifikationsgrößen des Bauelements erstellt worden sein (siehe physikalische Parametrierung). Die Bauelemente sind durch so genannte Flylines (Gummibänder) verbunden, die die noch nicht vorhandenen elektrischen Verbindungen darstellen. Der Layouter kann nun den Platzierungsvorschlag interaktiv bearbeiten und insbesondere die elektrischen Verbindungen entwurfsregelkorrekt verlegen.

Auch für diese Aufgabe wird Unterstützung vom Layoutwerkzeug zur Verfügung gestellt. Es können Leitungen vorgegebener Breite automatisch als rechtwinklige Pfade und zwischen den Ebenen durch automatisches Einfügen von Vias gezogen werden. Weiterhin können automatische Router (so genannte Point-to-Point-Router) für die Verlegung einzelner oder auch mehrerer Leitbahnen gleichzeitig eingesetzt werden.

Durch die Kopplung von Schematic und Layout wird neben der Vereinfachung des Entwurfsprozesses eine Korrektheit des Layouts sichergestellt, da weder Bauelemente noch Leitungen übersehen werden können.

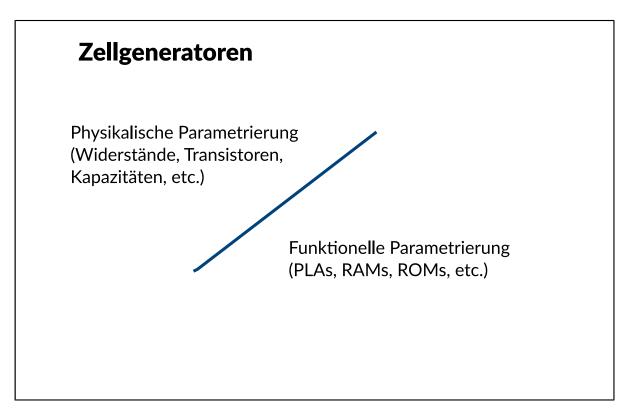

## Zellerzeugung: Zellgeneratoren

Die manuelle Erzeugung, auch von kleinen Layouts oder nur von Bauelementen aus einzelnen Polygonen in den unterschiedlichen Layern, ist fehleranfällig, mühsam und muss ständig wiederholt werden. Aus diesem Grunde sind Zellgeneratoren entwickelt worden, die für ein gegebenes Bauelement oder für kleine (meist digitale) Zellen das Layout automatisch erstellen. Zwei solcher Generatoren sind in den folgenden beiden Abschnitten beschrieben.

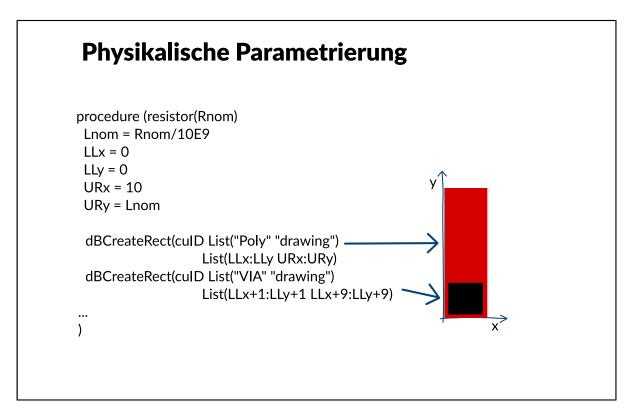

#### Zellerzeugung: Physikalische Parametrierung

Die einfachste Form der Parametrierung von Zellen erzeugt Layouts für die Basiselemente einer Schaltung also für Transistoren, Widerstände und Kondensatoren. Diese Zellen sind häufig in geometrischen Größen parametriert, wie in der Breite und der Länge des Kanals des MOS-Transistors. Elektrische Parameter können unter Kenntnis der Technologie verhältnismäßigleicht in geometrische umgerechnet werden. Diese geometrischen Größen sind direkt per Programm in Polygone umzusetzen. Ein Beispiel für den Code zur Erzeugung eines Widerstands ist im Bild gezeigt.

Das entstehende Layout ist im Bild rechts dargestellt. Neben den Layoutstrukturen für die elektrische Funktion können auch Kontakte, Schutzstrukturen wie Guardringe und Wannen generiert werden. Außerdem sind auch gefaltete und damit platzsparende Transistor-Layouts möglich, die bei großem W/L-Verhältnis (Kanalweite zu -länge) durch mäanderförmiges Verlegen des Gates erzeugt werden.

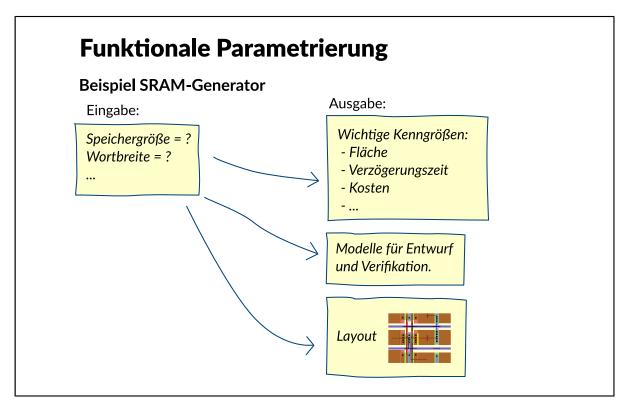

#### **Zellerzeugung: Funktionale Parametrierung**

Ein Höchstmaß an Flexibilität wird durch eine vollautomatische Generierung der Zellen erreicht. Der Benutzer spezifiziert dabei das Verhalten der Zelle mit Hilfe funktioneller Beschreibungen; hier genügt also nicht mehr eine einzelne Zahl. Ein Beispiel ist die Angabe einer booleschen Gleichung zur Definition eines PLAs. Typische Vertreter funktionell parametrierbarer Zellen sind PLA, RAM, ROM, Finite State Machine (FSM) bis hin zum mikroprogrammierbaren Mikroprozessor. Solche Zellgeneratoren verwenden vorwiegend, aber nicht ausschließlich, die Methode des Aneinandersetzens (butting) von Zellelementen. Oft sind dabei die Zellelemente selbst nicht mehr starr, sondern prozedural beschrieben. Ein wichtiger Aspekt des Generatorkonzepts besteht darin, dass nicht nur das Zelllayout, sondern gleichzeitig ein entsprechendes Simulationsmodell sowie die erforderlichen Testmuster generiert werden können. Ein grundsätzliches und noch nicht endgültig gelöstes Problem bei der Zellgenerierung ist die Sicherung der Gewährleistung von Zelleigenschaften: Feste Zellen, aber auch verschiedene Varianten von einfach parametrierbaren Zellen können probeweise gefertigt und vermessen werden. Dadurch wird sichergestellt, dass die durch elektrische Simulation ermittelten Zelleigenschaften auch auf einem realen Chip eingehalten werden. Bei der Vielfalt der Varianten frei generierbarer Zellen ist dies jedoch nicht erschöpfend möglich. Statistische Aussagen werden herangezogen.